# RapidIO<sup>™</sup> Interconnect Specification Part 6: 1x/4x LP-Serial Physical Layer Specification

Rev. 1.3, 06/2005

© Copyright RapidIO Trade Association

**RapidIO Trade Association**

### **Revision History**

| Revision | Description                                                                                                                                                                                                                                                                                                                                                                                                     | Date       |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 1.1      | First release                                                                                                                                                                                                                                                                                                                                                                                                   | 12/17/2001 |

| 1.2      | Technical changes: incorporate Rev. 1.1 errata rev. 1.1.1, errata 3                                                                                                                                                                                                                                                                                                                                             | 06/26/2002 |

| 1.3      | Technical changes: incorporate Rev 1.2 errata 1 as applicable,<br>the following errata showings:<br>03-03-00004.002, 03-07-00002.001, 03-12-00000.002, 03-12-00002.004,<br>04-02-00000.001, 04-05-00000.003, 04-05-00006.002 (partial), 04-05-00007.001<br>and the following new features showings:<br>02-03-0003.004, 02-06-00001.004, 04-08-00013.002, 04-09-00022.002<br>Converted to ISO-friendly templates | 02/23/2005 |

| 1.3      | Removed confidentiality markings for public release                                                                                                                                                                                                                                                                                                                                                             | 06/07/2005 |

NO WARRANTY.THE RAPIDIO TRADE ASSOCIATION PUBLISHES THE SPECIFICATION "AS IS". THE RAPIDIO TRADE ASSOCIATION MAKES NO WARRANTY, REPRESENTATION OR COVENANT, EXPRESS OR IMPLIED, OF ANY KIND CONCERNING THE SPECIFICATION, INCLUDING, WITHOUT LIMITATION, NO WARRANTY OF NON INFRINGEMENT, NO WARRANTY OF MERCHANTABILITY AND NO WARRANTY OF FITNESS FOR A PARTICULAR PURPOSE. USER AGREES TO ASSUME ALL OF THE RISKS ASSOCIATED WITH ANY USE WHATSOEVER OF THE SPECIFICATION. WITHOUT LIMITING THE GENERALITY OF THE FOREGOING, USER IS RESPONSIBLE FOR SECURING ANY INTELLECTUAL PROPERTY LICENSES OR RIGHTS WHICH MAY BE NECESSARY TO IMPLEMENT OR BUILD PRODUCTS COMPLYING WITH OR MAKING ANY OTHER SUCH USE OF THE SPECIFICATION.

DISCLAIMER OF LIABILITY. THE RAPIDIO TRADE ASSOCIATION SHALL NOT BE LIABLE OR RESPONSIBLE FOR ACTUAL, INDIRECT, SPECIAL, INCIDENTAL, EXEMPLARY OR CONSEQUENTIAL DAMAGES (INCLUDING, WITHOUT LIMITATION, LOST PROFITS) RESULTING FROM USE OR INABILITY TO USE THE SPECIFICATION, ARISING FROM ANY CAUSE OF ACTION WHATSOEVER, INCLUDING, WHETHER IN CONTRACT, WARRANTY, STRICT LIABILITY, OR NEGLIGENCE, EVEN IF THE RAPIDIO TRADE ASSOCIATION HAS BEEN NOTIFIED OF THE POSSIBILITY OF SUCH DAMAGES.

Questions regarding the RapidIO Trade Association, specifications, or membership should be forwarded to:

RapidIO Trade Association Suite 325, 3925 W. Braker Lane Austin, TX 78759 512-305-0070 Tel. 512-305-0009 FAX.

RapidIO and the RapidIO logo are trademarks and service marks of the RapidIO Trade Association. All other trademarks are the property of their respective owners.

#### **Chapter 1 Overview**

| 1.1  | Introduction                      | . 13 |

|------|-----------------------------------|------|

| 1.2  | Packets                           | . 14 |

| 1.3  | Control Symbols                   | . 14 |

| 1.4  | PCS and PMA Layers                | . 14 |

| 1.5  | LP-Serial Protocol                | . 15 |

| 1.6  | LP-Serial Registers               | . 15 |

| 1.7  | Signal Descriptions               | . 15 |

| 1.8  | AC Electrical Specifications      |      |

| 1.9  | Interface Management              | . 15 |

| 1.10 | System Resources                  | . 16 |

| 1.11 | Manufacturability and Testability | . 16 |

#### **Chapter 2 Packets**

| Introduction             | 17                                                                                   |

|--------------------------|--------------------------------------------------------------------------------------|

| Packet Field Definitions | 17                                                                                   |

| Packet Format            | 18                                                                                   |

| Packet Protection        | 18                                                                                   |

| Packet CRC Operation     | 19                                                                                   |

| 16-Bit Packet CRC Code   |                                                                                      |

| Maximum Packet Size      |                                                                                      |

|                          | Packet Format<br>Packet Protection<br>Packet CRC Operation<br>16-Bit Packet CRC Code |

#### **Chapter 3 Control Symbols**

| Introduction                       |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control Symbol Field Definitions   |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Control Symbol Format              |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Stype0 Control Symbols             |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Packet-Accepted Control Symbol     |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Packet-Retry Control Symbol        |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Packet-Not-Accepted Control Symbol |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Status Control Symbol              |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Link-Response Control Symbol       |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Stype1 Control Symbols             |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Start-of-Packet Control Symbol     |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Stomp Control Symbol               |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| End-of-Packet Control Symbol       |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Restart-From-Retry Control Symbol  |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Link-Request Control Symbol        |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Reset-Device Command               |                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                    | Control Symbol Field Definitions<br>Control Symbol Format<br>Stype0 Control Symbols<br>Packet-Accepted Control Symbol<br>Packet-Retry Control Symbol<br>Packet-Not-Accepted Control Symbol<br>Status Control Symbol<br>Link-Response Control Symbol<br>Stype1 Control Symbols<br>Start-of-Packet Control Symbol<br>Stomp Control Symbol<br>End-of-Packet Control Symbol<br>Restart-From-Retry Control Symbol<br>Link-Request Control Symbol |

| 3.5.5.2 | Input-Status Command           |  |

|---------|--------------------------------|--|

| 3.5.6   | Multicast-Event Control Symbol |  |

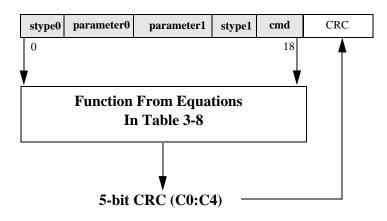

| 3.6     | Control Symbol Protection      |  |

| 3.6.1   | CRC-5 Code                     |  |

| 3.6.2   | CRC-5 Parallel Code Generation |  |

### Chapter 4 PCS and PMA Layers

| 4.1     | Introduction                            | 35 |

|---------|-----------------------------------------|----|

| 4.2     | PCS Layer Functions                     | 35 |

| 4.3     | PMA Layer Functions                     | 36 |

| 4.4     | Definitions                             | 36 |

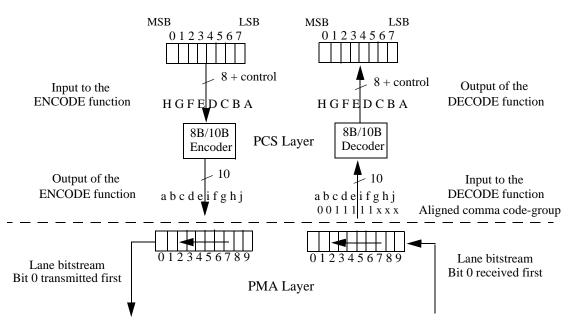

| 4.5     | 8B/10B Transmission Code                | 37 |

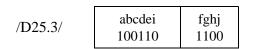

| 4.5.1   | Character and Code-Group Notation       | 37 |

| 4.5.2   | Running Disparity                       | 38 |

| 4.5.3   | Running Disparity Rules                 | 39 |

| 4.5.4   | 8B/10B Encoding                         | 39 |

| 4.5.5   | Transmission Order                      | 40 |

| 4.5.6   | 8B/10B Decoding                         | 41 |

| 4.5.7   | Special Characters and Columns          | 49 |

| 4.5.7.1 | Packet Delimiter Control Symbol (/PD/)  | 49 |

| 4.5.7.2 | Start of Control Symbol (/SC/)          | 50 |

| 4.5.7.3 | Idle (/I/)                              | 50 |

| 4.5.7.4 | Sync (/K/)                              |    |

| 4.5.7.5 | Skip (/R/)                              | 50 |

| 4.5.7.6 | Align (/A/)                             | 50 |

| 4.5.8   | Effect of Single Bit Code-Group Errors  | 51 |

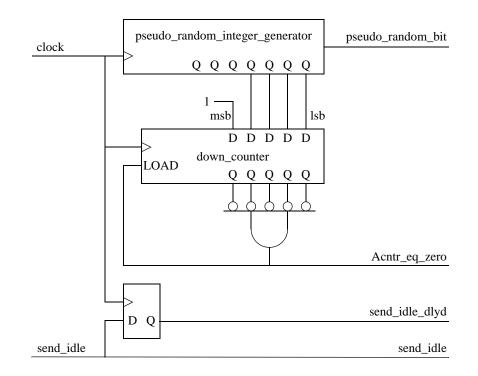

| 4.5.9   | Idle Sequence                           | 51 |

| 4.5.9.1 | Idle Sequence Generation                | 53 |

| 4.5.10  | 1x Link Transmission Rules              | 54 |

| 4.5.11  | 4x Link Striping and Transmission Rules | 56 |

| 4.6     | Retimers and Repeaters                  | 58 |

| 4.6.1   | Retimers                                |    |

| 4.6.2   | Repeaters                               | 59 |

| 4.7     | Port Initialization                     | 60 |

| 4.7.1   | 1x Mode Initialization                  | 60 |

| 4.7.2   | 1x/4x Mode Initialization               | 60 |

| 4.7.3   | State Machines                          | 61 |

| 4.7.3.1 | State Machine Conventions               | 61 |

| 4.7.3.2 | State Machine Variables and Functions   | 61 |

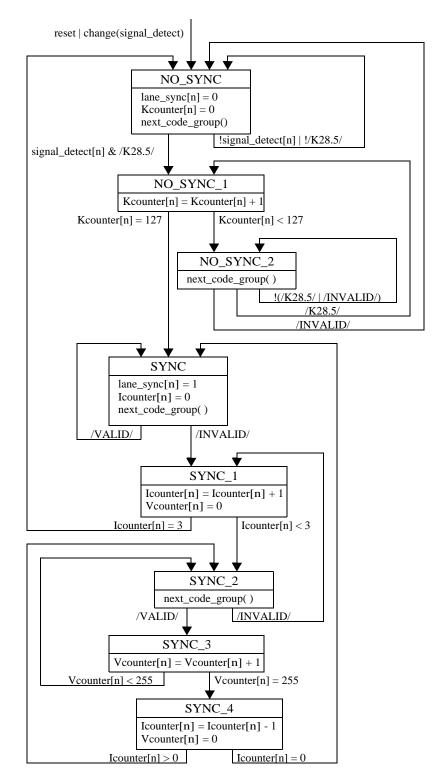

| 4.7.3.3 | Lane Synchronization State Machine      | 64 |

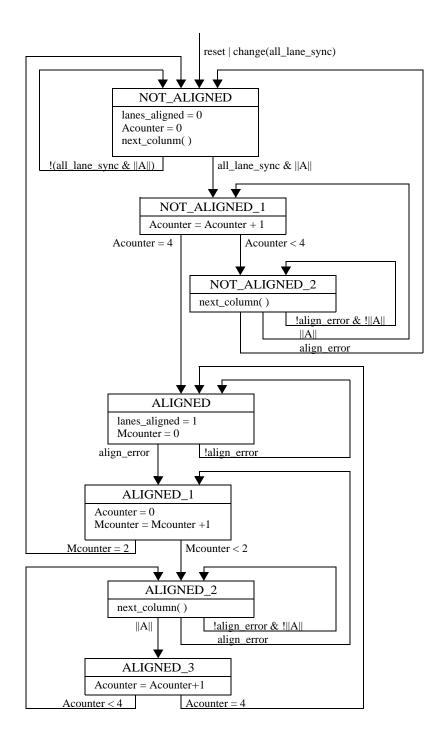

| 4.7.3.4 | Lane Alignment State Machine            |    |

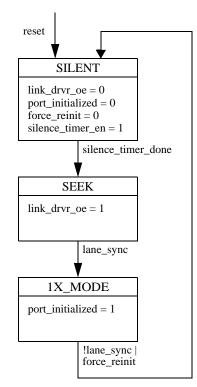

| 4.7.3.5 | 1x Mode Initialization State Machine    |    |

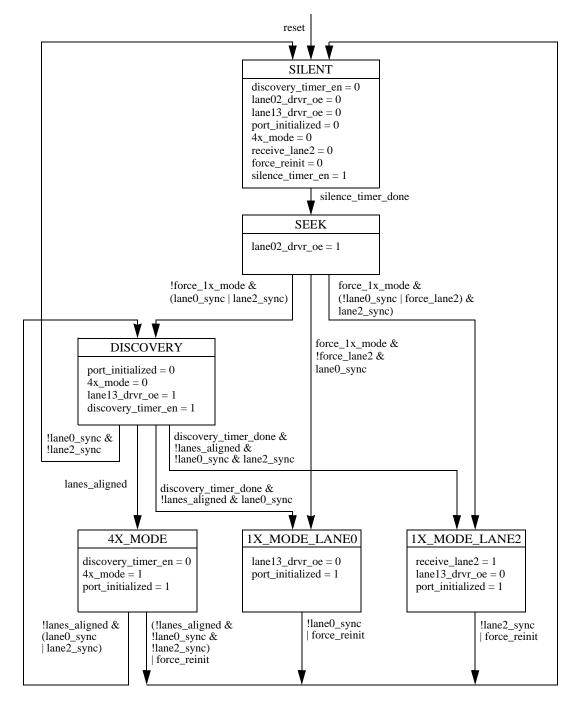

| 4.7.3.6 | 1x/4x Mode Initialization State Machine | 70 |

#### **Chapter 5 LP-Serial Protocol**

| 5.1        | Introduction                                   | 73 |

|------------|------------------------------------------------|----|

| 5.2        | Packet Exchange Protocol                       | 73 |

| 5.3        | Control Symbols                                | 74 |

| 5.3.1      | Control Symbol Delimiting                      | 74 |

| 5.3.2      | Control Symbol Transmission                    | 75 |

| 5.3.3      | Embedded Control Symbols                       | 75 |

| 5.3.4      | Multicast-Event Control Symbols                | 76 |

| 5.4        | Packets                                        | 77 |

| 5.4.1      | Packet Delimiting                              | 77 |

| 5.4.1.1    | Packet Start                                   | 77 |

| 5.4.1.2    | Packet Termination                             | 77 |

| 5.4.2      | Acknowledgment Identifier                      | 77 |

| 5.4.3      | Packet Priority and Transaction Request Flows  | 78 |

| 5.5        | Link Maintenance Protocol                      | 79 |

| 5.6        | Packet Transmission Protocol                   | 80 |

| 5.7        | Flow Control                                   | 82 |

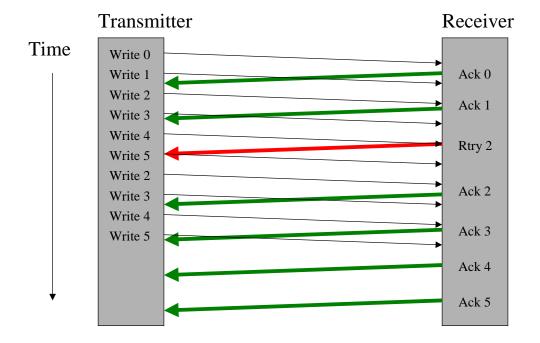

| 5.7.1      | Receiver-Controlled Flow Control               | 82 |

| 5.7.2      | Transmitter-Controlled Flow Control            | 84 |

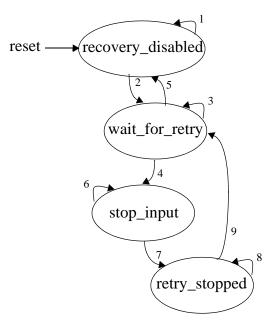

| 5.7.2.1    | Input Retry-Stopped Recovery Process           | 85 |

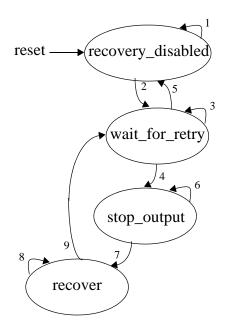

| 5.7.2.2    | Output Retry-Stopped Recovery Process          | 86 |

| 5.7.2.3    | Receive Buffer Management                      | 86 |

| 5.7.2.4    | Effective Number of Free Receive Buffers       |    |

| 5.7.2.5    | Speculative Packet Transmission                | 88 |

| 5.7.3      | Flow Control Mode Negotiation                  | 88 |

| 5.8        | Canceling Packets                              | 89 |

| 5.9        | Transaction and Packet Delivery Ordering Rules | 90 |

| 5.10       | Deadlock Avoidance                             | 91 |

| 5.11       | Error Detection and Recovery                   | 93 |

| 5.11.1     | Lost Packet Detection                          | 94 |

| 5.11.2     | Link Behavior Under Error                      | 94 |

| 5.11.2.1   | Recoverable Errors                             | 95 |

| 5.11.2.2   | Idle Sequence Errors                           | 95 |

| 5.11.2.3   | Control Symbol Errors                          | 95 |

| 5.11.2.3.1 | Link Protocol Violations                       | 96 |

| 5.11.2.3.2 | Corrupted Control symbols                      | 96 |

| 5.11.2.4   | Packet Errors                                  | 97 |

| 5.11.2.5   | Link Time-Out                                  | 97 |

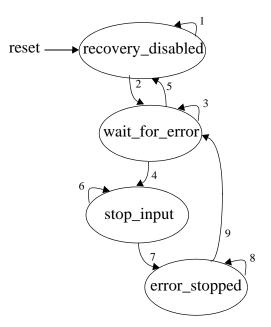

| 5.11.2.6   | Input Error-Stopped Recovery Process           | 97 |

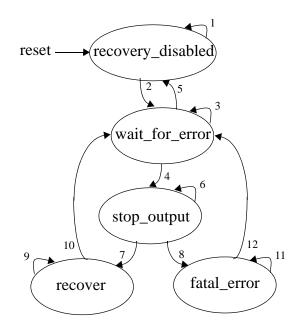

| 5.11.2.7   | Output Error-Stopped Recovery Process          | 98 |

| 5.12       | Power Management                               | 98 |

#### **Chapter 6 LP-Serial Registers**

| 6.1     | Introduction                                                            | 99  |

|---------|-------------------------------------------------------------------------|-----|

| 6.2     | Register Map                                                            | 99  |

| 6.3     | Reserved Register and Bit Behavior                                      | 100 |

| 6.4     | Capability Registers (CARs)                                             | 102 |

| 6.4.1   | Processing Element Features CAR (Configuration Space Offset 0x10)       | 102 |

| 6.5     | Generic End Point Devices                                               | 103 |

| 6.5.1   | Register Map                                                            | 103 |

| 6.5.2   | Command and Status Registers (CSRs)                                     | 105 |

| 6.5.2.1 | 1x/4x LP-Serial Register Block Header (Block Offset 0x0)                | 105 |

| 6.5.2.2 | Port Link Time-out Control CSR (Block Offset 0x20)                      | 105 |

| 6.5.2.3 | Port Response Time-out Control CSR (Block Offset 0x24)                  | 106 |

| 6.5.2.4 | Port General Control CSR (Block Offset 0x3C)                            | 106 |

| 6.5.2.5 | Port n Error and Status CSRs (Block Offsets 0x58, 78,, 238)             |     |

| 6.5.2.6 | Port n Control CSR (Block Offsets 0x5C, 7C,, 23C)                       |     |

| 6.6     | Generic End Point Devices, software assisted error recovery option      | 110 |

| 6.6.1   | Register Map                                                            |     |

| 6.6.2   | Command and Status Registers (CSRs)                                     | 112 |

| 6.6.2.1 | 1x/4x LP-Serial Register Block Header (Block Offset 0x0)                | 112 |

| 6.6.2.2 | Port Link Time-out Control CSR (Block Offset 0x20)                      | 112 |

| 6.6.2.3 | Port Response Time-out Control CSR (Block Offset 0x24)                  | 113 |

| 6.6.2.4 | Port General Control CSR (Block Offset 0x3C)                            |     |

| 6.6.2.5 | Port n Link Maintenance Request CSRs                                    |     |

|         | (Block Offsets 0x40, 60,, 220)                                          | 114 |

| 6.6.2.6 | Port n Link Maintenance Response CSRs                                   |     |

|         | (Block Offsets 0x44, 64,, 224)                                          | 114 |

| 6.6.2.7 | Port n Local ackID CSRs (Block Offsets 0x48, 68,, 228)                  | 114 |

| 6.6.2.8 | Port n Error and Status CSRs (Block Offset 0x58, 78,, 238)              | 115 |

| 6.6.2.9 | Port n Control CSR (Block Offsets 0x5C, 7C,, 23C)                       | 116 |

| 6.7     | Generic End Point Free Devices                                          | 119 |

| 6.7.1   | Register Map                                                            | 119 |

| 6.7.2   | Command and Status Registers (CSRs)                                     | 120 |

| 6.7.2.1 | 1x/4x LP-Serial Register Block Header (Block Offset 0x0)                | 120 |

| 6.7.2.2 | Port Link Time-out Control CSR (Block Offset 0x20)                      | 120 |

| 6.7.2.3 | Port General Control CSR (Block Offset 0x3C)                            | 121 |

| 6.7.2.4 | Port n Error and Status CSRs (Block Offsets 0x58, 78,, 238)             |     |

| 6.7.2.5 | Port n Control CSR (Block Offsets 0x5C, 7C,, 23C)                       | 122 |

| 6.8     | Generic End Point Free Devices, software assisted error recovery option | 125 |

| 6.8.1   | Register Map                                                            |     |

| 6.8.2   | Command and Status Registers (CSRs)                                     | 127 |

| 6.8.2.1 | 1x/4x LP-Serial Register Block Header (Block Offset 0x0)                |     |

| 6.8.2.2 | Port Link Time-out Control CSR (Block Offset 0x20)                      |     |

| 6.8.2.3 | Port General Control CSR (Block Offset 0x3C)                            | 128 |

| 6.8.2.4 | Port n Link Maintenance Request CSRs                                    |     |

|         | (Block Offsets 0x40, 60,, 220)                                          | 128 |

| 6.8.2.5 | Port n Link Maintenance Response CSRs                      |     |

|---------|------------------------------------------------------------|-----|

|         | (Block Offsets 0x44, 64,, 224)                             | 128 |

| 6.8.2.6 | Port n Local ackID CSRs (Block Offsets 0x48, 68,, 228)     | 129 |

| 6.8.2.7 | Port n Error and Status CSRs (Block Offset 0x58, 78,, 238) | 129 |

| 6.8.2.8 | Port n Control CSR (Block Offsets 0x5C, 7C,, 23C)          | 130 |

#### **Chapter 7 Signal Descriptions**

| 7.1 | Introduction                      | 133 |

|-----|-----------------------------------|-----|

| 7.2 | Signal Definitions                | 133 |

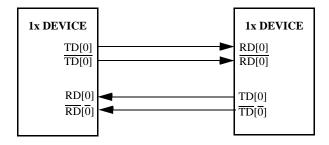

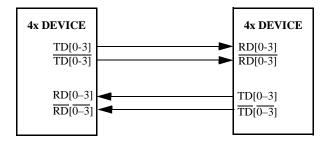

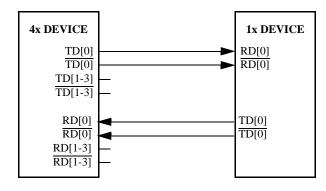

| 7.3 | Serial RapidIO Interface Diagrams | 134 |

#### **Chapter 8 Electrical Specifications**

| 8.1   | Introduction                                                | 135 |

|-------|-------------------------------------------------------------|-----|

| 8.2   | Signal Definitions                                          | 136 |

| 8.3   | Equalization                                                | 137 |

| 8.4   | Explanatory Note on Transmitter and Receiver Specifications | 137 |

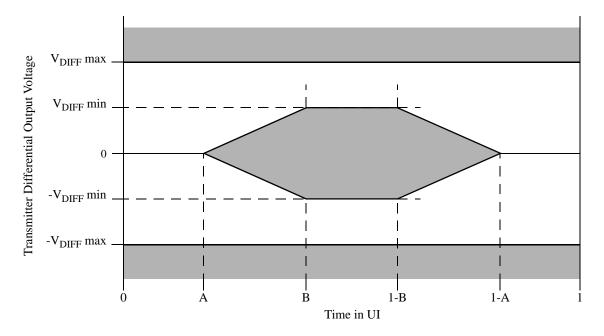

| 8.5   | Transmitter Specifications                                  | 138 |

| 8.6   | Receiver Specifications                                     | 142 |

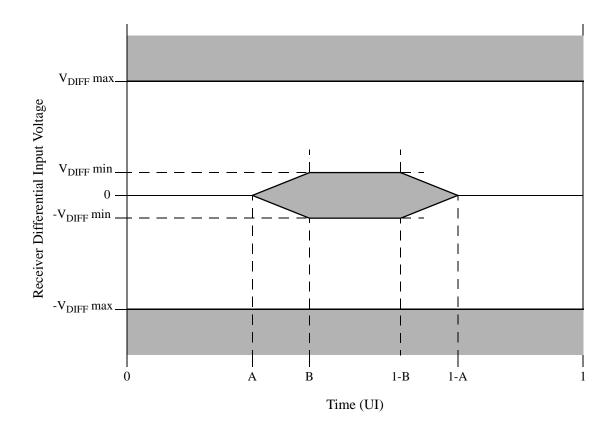

| 8.7   | Receiver Eye Diagrams                                       | 145 |

| 8.8   | Measurement and Test Requirements                           | 146 |

| 8.8.1 | Eye template measurements                                   | 146 |

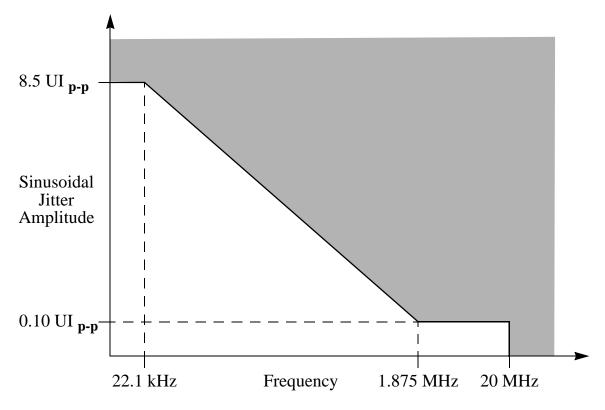

| 8.8.2 | Jitter test measurements                                    | 146 |

| 8.8.3 | Transmit jitter                                             | 146 |

| 8.8.4 | Jitter tolerance                                            | 147 |

#### Annex A Interface Management (Informative)

| 149 |

|-----|

| 151 |

|     |

| 153 |

|     |

| •   |

#### Annex B Critical Resource Performance Limits (Informative)

#### Annex C Manufacturability and Testability (Informative)

Blank page

# **List of Figures**

| 2-2  | Packet Alignment                                                    |    |

|------|---------------------------------------------------------------------|----|

| 2-1  | Packet Format                                                       | 18 |

| 2-3  | Error Coverage of First 16 Bits of Packet Header                    | 19 |

| 2-4  | Unpadded Packet of Length 80 Bytes or Less                          |    |

| 2-5  | Padded Packet of Length 80 Bytes or Less                            |    |

| 2-6  | Unpadded Packet of Length Greater than 80 Bytes                     |    |

| 2-7  | Padded Packet of Length Greater than 80 Bytes                       | 21 |

| 2-8  | CRC Generation Pipeline                                             |    |

| 3-1  | Packet-Retry Control Symbol Format                                  | 25 |

| 3-2  | Packet-Accepted Control Symbol Format                               |    |

| 3-3  | Packet-Retry Control Symbol Format                                  |    |

| 3-4  | Packet-Not-Accepted Control Symbol Format                           |    |

| 3-5  | Status Control Symbol Format                                        |    |

| 3-6  | Link-Response Control Symbol Format                                 |    |

| 3-7  | Start-of-Packet Control Symbol Format                               |    |

| 3-8  | Stomp Control Symbol Format                                         |    |

| 3-9  | End-of-Packet Control Symbol Format                                 |    |

| 3-10 | Restart-From-Retry Control Symbol Format                            |    |

| 3-11 | Link-Request Control Symbol Format                                  |    |

| 3-12 | Multicast-Event Control Symbol Format                               |    |

| 3-13 | 5-bit CRC Implementation                                            |    |

| 4-1  | Character Notation Example (D25.3)                                  |    |

| 4-2  | Code-Group Notation Example (/D25.3/)                               |    |

| 4-3  | Lane Encoding, Serialization, Deserialization, and Decoding Process |    |

| 4-4  | Example of a Pseudo-Random Idle Code-Group Generator                | 53 |

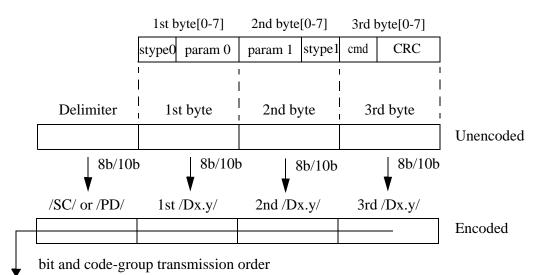

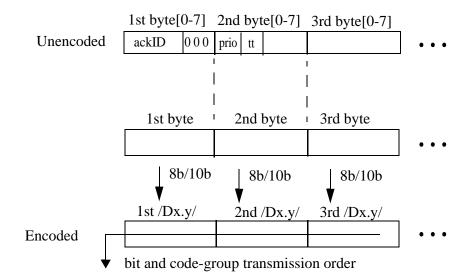

| 4-5  | 1x Mode Control Symbol Encoding and Transmission Order              | 54 |

| 4-6  | 1x Mode Packet Encoding and Transmission Order                      | 55 |

| 4-7  | 1x Typical Data Flow                                                | 56 |

| 4-8  | Typical 4x Data Flow                                                |    |

| 4-9  | Lane_Synchronization State                                          | 66 |

| 4-10 | Lane_Alignment State Machine                                        | 68 |

| 4-11 | 1x_Initialization State Machine                                     | 70 |

| 4-12 | 1x/4x_Initialization State Machine                                  | 72 |

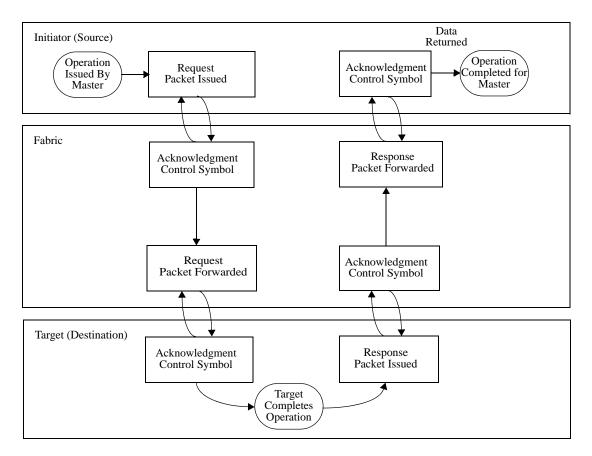

| 5-1  | Example Transaction with Acknowledgment                             | 74 |

| 5-2  | Receiver-Controlled Flow Control                                    |    |

| 5-3  | Transmitter-Controlled Flow Control                                 |    |

| 7-1  | RapidIO 1x Device to 1x Device Interface Diagram                    |    |

| 7-2  | RapidIO 4x Device to 4x Device Interface Diagram                    |    |

| 7-3  | RapidIO 4x Device to 1x Device Interface Diagram                    |    |

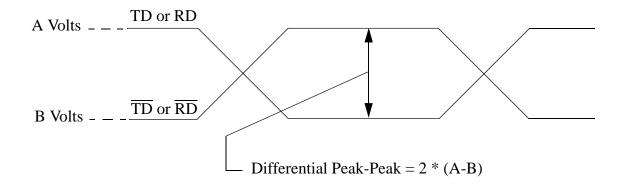

| 8-1  | Differential Peak-Peak Voltage of Transmitter or Receiver           |    |

| 8-2  | Transmitter Output Compliance Mask                                  |    |

# **List of Figures**

| Single Frequency Sinusoidal Jitter Limits | 144                            |

|-------------------------------------------|--------------------------------|

| Receiver Input Compliance Mask            | 145                            |

| Input Port Retry Recovery State Machine   |                                |

| Output Port Retry Recovery State Machine  | 151                            |

|                                           |                                |

| 1 2                                       |                                |

|                                           | Receiver Input Compliance Mask |

# List of Tables

| 2-1  | Packet Field Definitions                                               | 17  |

|------|------------------------------------------------------------------------|-----|

| 2-2  | Parallel CRC Intermediate Value Equations                              | 21  |

| 2-3  | Maximum Packet Size                                                    | 23  |

| 3-1  | Control Symbol Field Definitions                                       | 25  |

| 3-2  | Stype0 Control Symbol Encoding                                         |     |

| 3-3  | Stype0 Parameter Definitions                                           | 27  |

| 3-4  | Cause Field Definition                                                 |     |

| 3-5  | Port_status Field Definitions                                          | 29  |

| 3-6  | Stype1 Control Symbol Encoding                                         |     |

| 3-7  | Cmd Field Definitions                                                  |     |

| 3-8  | Parallel CRC Equations                                                 |     |

| 4-1  | Data Character Encodings                                               | 41  |

| 4-2  | Special Character Encodings                                            | 48  |

| 4-3  | Special Characters and Columns                                         |     |

| 4-4  | Code-Group Corruption Caused by Single Bit Errors                      | 51  |

| 5-1  | Transaction Request Flow to Priority Mapping                           |     |

| 5-2  | Transaction Request Flow to Priority and Critical Request Flow Mapping | 78  |

| 6-1  | 1x/4x LP-Serial Register Map                                           |     |

| 6-2  | Configuration Space Reserved Access Behavior                           |     |

| 6-3  | Bit Settings for Processing Element Features CAR                       |     |

| 6-4  | LP-Serial Register Map - Generic End Point Devices                     |     |

| 6-5  | Bit Settings for 1x/4x LP-Serial Register Block Header                 | 105 |

| 6-6  | Bit Settings for Port Link Time-out Control CSR                        | 105 |

| 6-7  | Bit Settings for Port Response Time-out Control CSR                    | 106 |

| 6-8  | Bit Settings for Port General Control CSRs                             | 106 |

| 6-9  | Bit Settings for Port n Error and Status CSRs                          | 107 |

| 6-10 | Bit Settings for Port n Control CSRs                                   |     |

| 6-11 | LP-Serial Register Map - Generic End Point Devices (SW assisted)       | 110 |

| 6-12 | Bit Settings for 1x/4x LP-Serial Register Block Header                 | 112 |

| 6-13 | Bit Settings for Port Link Time-out Control CSR                        |     |

| 6-14 | Bit Settings for Port Response Time-out Control CSR                    |     |

| 6-15 | Bit Settings for Port General Control CSRs                             |     |

| 6-16 | Bit Settings for Port n Link Maintenance Request CSRs                  | 114 |

| 6-17 | Bit Settings for Port n Link Maintenance Response CSRs                 | 114 |

| 6-18 | Bit Settings for Port n Local ackID Status CSRs                        |     |

| 6-19 | Bit Settings for Port n Error and Status CSRs                          | 115 |

| 6-20 | Bit Settings for Port n Control CSRs                                   | 116 |

| 6-21 | LP-Serial Register Map - Generic End Point Free Devices                | 119 |

| 6-22 | Bit Settings for 1x/4x LP-Serial Register Block Header                 |     |

| 6-23 | Bit Settings for Port Link Time-out Control CSR                        |     |

| 6-24 | Bit Settings for Port General Control CSRs                             |     |

| 6-25 | Bit Settings for Port n Error and Status CSRs                          | 121 |

# **List of Tables**

| 6-26 | Bit Settings for Port n Control CSRs                                     | .122 |

|------|--------------------------------------------------------------------------|------|

| 6-27 | LP-Serial Register Map - Generic End Point-free Devices (SW assisted)    | .125 |

| 6-28 | Bit Settings for 1x/4x LP-Serial Register Block Header                   | .127 |

| 6-29 | Bit Settings for Port Link Time-out Control CSR                          | .127 |

| 6-30 | Bit Settings for Port General Control CSRs                               | .128 |

| 6-31 | Bit Settings for Port n Link Maintenance Request CSRs                    | .128 |

| 6-32 | Bit Settings for Port n Link Maintenance Response CSRs                   | .128 |

| 6-33 | Bit Settings for Port n Local ackID Status CSRs                          | .129 |

| 6-34 | Bit Settings for Port n Error and Status CSRs                            | .129 |

| 6-35 | Bit Settings for Port n Control CSRs                                     | .130 |

| 7-1  | 1x/4x LP-Serial Signal Description                                       | .133 |

| 8-1  | Short Run Transmitter AC Timing Specifications - 1.25 GBaud              | .138 |

| 8-2  | Short Run Transmitter AC Timing Specifications - 2.5 GBaud               | .138 |

| 8-3  | Short Run Transmitter AC Timing Specifications - 3.125 GBaud             | .139 |

| 8-4  | Long Run Transmitter AC Timing Specifications - 1.25 GBaud               | .139 |

| 8-5  | Long Run Transmitter AC Timing Specifications - 2.5 GBaud                | .140 |

| 8-6  | Long Run Transmitter AC Timing Specifications - 3.125 GBaud              | .140 |

| 8-7  | Transmitter Differential Output Eye Diagram Parameters                   | .141 |

| 8-8  | Receiver AC Timing Specifications - 1.25 GBaud                           | .142 |

| 8-9  | Receiver AC Timing Specifications - 2.5 GBaud                            | .142 |

| 8-10 | Receiver AC Timing Specifications - 3.125 GBaud                          | .143 |

| 8-11 | Receiver Input Compliance Mask Parameters exclusive of Sinusoidal Jitter | .145 |

| A-1  | Input Port Retry Recovery State Machine Transition Table                 |      |

| A-2  | Output Port Retry Recovery State Machine Transition Table                | .152 |

| A-3  | Input Port Error Recovery State Machine Transition Table                 | .154 |

| A-4  | Output Port Error Recovery State Machine Transition Table                | .155 |

| B-12 | Packet Transmission Delay Components                                     | .160 |

| B-13 | Packet Acknowledgment Delay Components                                   | .161 |

| B-14 | Packet Delays                                                            |      |

| B-15 | Maximum Transmission Distances                                           | .162 |

# **Chapter 1 Overview**

### **1.1 Introduction**

The *RapidIO Part 6: 1x/4x LP-Serial Physical Layer Specification* addresses the physical layer requirements for devices utilizing an electrical serial connection medium. This specification defines a full duplex serial physical layer interface (link) between devices using unidirectional differential signals in each direction. Further, it allows ganging of four serial links for applications requiring higher link performance. It also defines a protocol for link management and packet transport over a link.

RapidIO systems are comprised of end point processing elements and switch processing elements. The RapidIO interconnect architecture is partitioned into a layered hierarchy of specifications which includes the Logical, Common Transport, and Physical layers. The Logical layer specifications define the operations and associated transactions by which end point processing elements communicate with each other. The Common Transport layer defines how transactions are routed from one end point processing element to another through switch processing elements. The Physical Layer defines how adjacent processing elements electrically connect to each other. RapidIO packets are formed through the combination of bit fields defined in the Logical, Common Transport, and Physical Layer specifications.

The RapidIO 1x/4x LP-Serial specification defines a protocol for packet delivery between serial RapidIO devices including packet and control symbol transmission, flow control, error management, and other device to device functions. A particular device may not implement all of the mode selectable features found in this document. See the appropriate user's manual or implementation specification for specific implementation details of a device.

The 1x/4x LP-Serial physical layer specification has the following properties:

- Embeds the transmission clock with data using an 8B/10B encoding scheme.

- Supports one serial differential pair, referred to as one lane, or four ganged serial differential pairs, referred to as four lanes, in each direction.

- Allows switching packets between RapidIO 1x/4x LP-Serial ports and *RapidIO Part 4: 8/16 LP-LVDS Physical Layer Specification* ports without requiring packet manipulation.

- Employs similar retry and error recovery protocols as the RapidIO 8/16 LP-LVDS physical layer specification.

• Supports transmission rates of 1.25, 2.5, and 3.125 Gbaud (data rates of 1.0, 2.0, and 2.5 Gbps) per lane.

This specification first defines the individual elements that make up the link protocol such as packets, control symbols, and the serial bit encoding scheme. This is followed by a description of the link protocol. Finally, the control and status registers, signal descriptions, and electrical specifications are specified.

### **1.2 Packets**

Chapter 2, "Packets" defines how a RapidIO 1x/4x LP-Serial packet is formed by prefixing a 10-bit physical layer header to the combined RapidIO transport and logical layer bit fields followed by an appended 16-bit CRC field.

This chapter shows the packet header format, the packet field definitions, the CRC error detection mechanism, and the packet alignment rules necessary to form LP-Serial packets.

# **1.3 Control Symbols**

Chapter 3, "Control Symbols" defines the format of the two classes of control symbols (stype0 and stype1) used for packet acknowledgment, link utility functions, link maintenance, and packet delineation. A control symbol is a 24-bit entity (including a 5-bit CRC code). The control symbol is used for packet delineation and may also be embedded within a packet as well as sent when the link is idle.

Acknowledgment control symbols are used by processing elements to indicate packet transmission status. Utility control symbols are used to communicate buffer status and link recovery synchronization. Link maintenance control symbols are used by adjacent devices to communicate physical layer status, synchronization requests, and device reset.

# **1.4 PCS and PMA Layers**

Chapter 4, "PCS and PMA Layers" describes the Physical Coding Sublayer (PCS) functionality as well as the Physical Media Attachment (PMA) functionality. The PCS layer functionality includes 8B/10B encoding scheme for embedding clock with data. It also gives transmission rules for the 1x and 4x interfaces and defines the link initialization sequence for clock synchronization.

The PMA (Physical Medium Attachment) function is responsible for serializing the 10-bit code-groups to and from the serial bitstream(s).

# **1.5 LP-Serial Protocol**

Chapter 5, "LP-Serial Protocol" describes in detail how packets, control symbols, and the PCS/PMA layers are used to implement the physical layer protocol. This includes topics such as link initialization, link maintenance, error detection and recovery, flow control, and transaction delivery ordering.

# **1.6 LP-Serial Registers**

Chapter 6, "LP-Serial Registers" describes the physical layer control and status register set. By accessing these registers a processing element may query the capabilities and status and configure another 1x/4x LP-Serial RapidIO processing element.

These registers utilize the Extended Features blocks and are accessed using *RapidIO Part 1: Input/Output Logical Specification* maintenance operations. Four types of RapidIO devices are defined in this section as follows:

- Generic End Point Processing Elements

- Generic End Point Processing Elements with software assisted error recovery

- Generic End Point Free Processing Elements (typically switch processing elements)

- Generic End Point Free Processing Elements with software assisted error recovery

# **1.7 Signal Descriptions**

Chapter 7, "Signal Descriptions" contains the signal pin descriptions for a RapidIO LP-Serial end point device and shows connectivity between processing elements with 1x ports and processing elements with 4x ports.

# **1.8 AC Electrical Specifications**

Chapter 8, "Electrical Specifications" describes the electrical specifications for the RapidIO 1x/4x LP-Serial device. This section defines two transmission types; short run and long run, as well as three speed grades (1.25 GHz, 2.5 GHz, and 3.125 GHz). This section also shows the required receiver eye diagrams for each link speed.

### **1.9 Interface Management**

Annex A, "Interface Management (Informative)" contains information pertinent to interface management in a RapidIO system, including error recovery, link initialization, and packet retry state machines.

# **1.10 System Resources**

Annex B, "Critical Resource Performance Limits (Informative)" contains a discussion on outstanding transactions and their relationship to transmission distance capability.

### 1.11 Manufacturability and Testability

Section Annex C, "Manufacturability and Testability (Informative)" recommends implementing to IEEE standard 1149.6 for improved manufacturing and manufacturing test.

# **Chapter 2 Packets**

### 2.1 Introduction

This chapter specifies the LP-Serial packet format and the fields that are added by LP-Serial physical layer. These packets are fed into the PCS function explained in Chapter 4, "PCS and PMA Layers".

### 2.2 Packet Field Definitions

This section specifies the bit fields added to a packet by the LP-Serial physical layer. These fields are required to implement the flow control, error management, and other specified system functions of the LP-Serial specification. The fields are specified in Table 2-1.

| Field | Description                                                                                                                                                                                                                        |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ackID | Acknowledge ID is the packet identifier for acknowledgments back to the packet sender—see Section 5.4.2 for details concerning ackID functionality.                                                                                |

| rsvd  | The reserved bits are set to logic 0 when the packet is generated and ignored when a packet is received.                                                                                                                           |

| prio  | Sets packet priority:<br>0b00 - lowest priority<br>0b01 - medium priority<br>0b10 - high priority<br>0b11 - highest priority<br>See Section 5.4.3 for an explanation of prioritizing packets                                       |

| CRF   | Critical Request Flow is an optional bit that differentiates between flows of<br>equal priority<br>If Critical Request Flow is not supported, this bit is reserved<br>See Section 5.4.3 for an explanation of prioritizing packets |

| CRC   | Cyclic Redundancy Code used to detect transmission errors in the packet. See<br>Section 2.4.1 for details on the CRC error detection scheme.                                                                                       |

**Table 2-1. Packet Field Definitions**

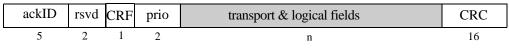

# 2.3 Packet Format

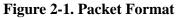

This section specifies the format of a LP-Serial packets. Figure 2-1 shows the format of the LP-Serial packet and how the physical layer ackID, rsvd, CRF, and prio fields are prefixed at the beginning of the packet and the 16-bit CRC field is appended to the end of the packet.

The unshaded fields are the fields added by the physical layer. The shaded field is the combined logical and transport layer bits and fields that are passed to the physical layer. The 2-bit rsvd field is required to make the packet length an integer multiple of 16 bits.

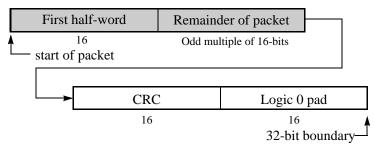

LP-Serial packets shall have a length that is an integer multiple of 32 bits. This sizing simplifies the design of port logic whose internal data paths are an integer multiple of 32 bits in width. Packets, as defined in this specification and the appropriate logical and transport layer specifications, have a length that is an integer multiple of 16 bits. This is illustrated in Figure 2-2. If the length of a packet defined by the above combination of specifications is an odd multiple of 16 bits, a 16-bit pad whose value is 0 (0x0000) shall be appended at the end of the packet such that the resulting padded packet is an integer multiple of 32 bits in length.

Figure 2-2. Packet Alignment

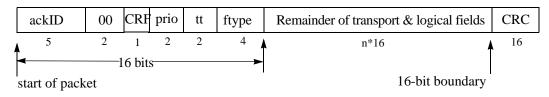

# 2.4 Packet Protection

A 16-bit CRC code is added to each packet by the LP-Serial physical layer to provide error detection. The code covers the entire packet except for the ackID field and one bit of the rsvd field, which are considered to be zero for the CRC calculations. Figure 2-3 shows the CRC coverage for the first 16 bits of the packet which contain the bits not covered by the code.

This structure allows the ackID to be changed on a link-by-link basis as the packet is transported across the fabric without requiring that the CRC be recomputed for each link. Since ackIDs on each link are assigned sequentially for each subsequent transmitted packet, an error in the ackID field is easily detected.

#### Figure 2-3. Error Coverage of First 16 Bits of Packet Header

### 2.4.1 Packet CRC Operation

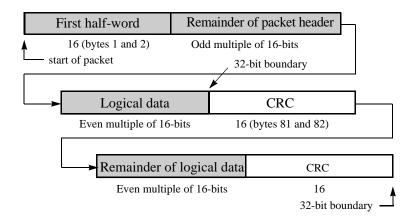

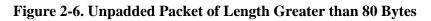

The CRC is appended to a packet in one of two ways. For a packet whose length, exclusive of CRC, is 80 bytes or less, a single CRC is appended at the end of the logical fields. For packets whose length, exclusive of CRC, is greater than 80 bytes, a CRC is added after the first 80 bytes and a second CRC is appended at the end of the logical layer fields.

The second CRC value is a continuation of the first. The first CRC is included in the running calculation, meaning that the running CRC value is not reinitialized after it is inserted after the first 80 bytes of the packet. This allows intervening devices to regard the embedded CRC value as two bytes of packet payload for CRC checking purposes. If the CRC appended to the end of the logical layer fields does not cause the end of the resulting packet to align to a 32-bit boundary, a two byte pad of all logic 0s is postpended to the packet. The pad of logic 0s allows the CRC check to always be done at the 32-bit boundary. A corrupt pad may or may not cause a CRC error to be detected, depending upon the implementation.

The early CRC value can be used by the receiving processing element to validate the header of a large packet and start processing the data before the entire packet has been received, freeing up resources earlier and reducing transaction completion latency.

#### NOTE:

While the embedded CRC value can be used by a processing element to start processing the data within a packet before receiving the entire packet, it is possible that upon reception of the end of the packet the final CRC value for the packet is incorrect. This would result in a processing element that has processed data that may have been corrupted. Outside of the error recovery mechanism described in Section 5.11.2, the RapidIO Interconnect Specification does not address the occurrence of such situations nor does it suggest a means by which a processing element would handle such situations. Instead, the mechanism for handling this situation is left to be addressed by the device manufacturers for devices that implement the functionality of early processing of packet data.

Figure 2-4 is an example of an unpadded packet of length less than or equal to 80 bytes.

| First half-word | Remainder of packet      | CRC             |

|-----------------|--------------------------|-----------------|

| 16              | Even multiple of 16-bits | 16              |

| start of packet | ĩ                        | 32-bit boundary |

Figure 2-4. Unpadded Packet of Length 80 Bytes or Less

Figure 2-5 is an example of a padded packet of length less than or equal to 80 bytes.

Figure 2-5. Padded Packet of Length 80 Bytes or Less

Figure 2-6 is an example of an unpadded packet of length greater than 80 bytes.

Figure 2-7 is an example of a padded packet of length greater than 80 bytes.

Figure 2-7. Padded Packet of Length Greater than 80 Bytes

### 2.4.2 16-Bit Packet CRC Code

The ITU polynomial  $X^{16}+X^{12}+X^{5}+1$  shall be used to generate the 16-bit CRC for packets. The value of the CRC shall be initialized to 0xFFFF (all logic 1s) at the beginning of each packet. For the CRC calculation, the uncovered six bits are treated as logic 0s. As an example, a 16-bit wide parallel calculation is described in the equations in Table 2-2. Equivalent implementations of other widths can be employed.

| Check Bit | e<br>0<br>0 | e<br>0<br>1 | e<br>0<br>2 | e<br>0<br>3 | e<br>0<br>4 | e<br>0<br>5 | e<br>0<br>6 | e<br>0<br>7 | e<br>0<br>8 | e<br>0<br>9 | e<br>1<br>0 | e<br>1<br>1 | e<br>1<br>2 | e<br>1<br>3 | e<br>1<br>4 | e<br>1<br>5 |

|-----------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| C00       |             |             |             |             | х           | х           |             |             | х           |             |             |             | х           |             |             |             |

| C01       |             |             |             |             |             | х           | х           |             |             | х           |             |             |             | х           |             |             |

| C02       |             |             |             |             |             |             | х           | х           |             |             | х           |             |             |             | х           |             |

| C03       | х           |             |             |             |             |             |             | х           | х           |             |             | х           |             |             |             | х           |

| C04       | х           | х           |             |             | х           | х           |             |             |             | х           |             |             |             |             |             |             |

| C05       |             | х           | х           |             |             | х           | х           |             |             |             | х           |             |             |             |             |             |

| C06       | х           |             | х           | х           |             |             | х           | х           |             |             |             | х           |             |             |             |             |

| C07       | х           | х           |             | х           | х           |             |             | х           | х           |             |             |             | х           |             |             |             |

| C08       | х           | х           | х           |             | х           | х           |             |             | х           | х           |             |             |             | х           |             |             |

| C09       |             | х           | х           | х           |             | х           | х           |             |             | х           | х           |             |             |             | х           |             |

| C10       |             |             | х           | х           | х           |             | х           | x           |             |             | х           | х           |             |             |             | х           |

| C11       | х           |             |             | х           |             |             |             | х           |             |             |             | х           |             |             |             |             |

| C12       | х           | х           |             |             | х           |             |             |             | х           |             |             |             | х           |             |             |             |

Table 2-2. Parallel CRC Intermediate Value Equations

| Check Bit | e<br>0<br>0 | e<br>0<br>1 | e<br>0<br>2 | e<br>0<br>3 | e<br>0<br>4 | e<br>0<br>5 | e<br>0<br>6 | e<br>0<br>7 | e<br>0<br>8 | e<br>0<br>9 | e<br>1<br>0 | e<br>1<br>1 | e<br>1<br>2 | e<br>1<br>3 | e<br>1<br>4 | e<br>1<br>5 |

|-----------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| C13       |             | х           | х           |             |             | х           |             |             |             | х           |             |             |             | х           |             |             |

| C14       |             |             | х           | х           |             |             | х           |             |             |             | х           |             |             |             | х           |             |

| C15       |             |             |             | х           | X           |             |             | х           |             |             |             | х           |             |             |             | x           |

Table 2-2. Parallel CRC Intermediate Value Equations (Continued)

where:

| C00–C15 | contents of the new check symbol          |

|---------|-------------------------------------------|

| e00-e15 | contents of the intermediate value symbol |

|         | e00 = d00  XOR  c00                       |

|         | e01 = d01  XOR  c01                       |

|         | through                                   |

|         | e15 = d15  XOR  c15                       |

- d00–d15 contents of the next 16 bits of the packet

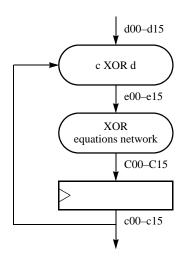

- c00–c15 contents of the previous check symbol assuming the pipeline described in Figure 2-8

Figure 2-8. CRC Generation Pipeline

# 2.5 Maximum Packet Size

The maximum packet size permitted by the LP-Serial specification is 276 bytes. This includes all packet logical, transport, and physical layer header information, data payload, and required CRC bytes.

The maximum packet size of 276 bytes is achieved as shown below:

Table 2-3. Maximum Packet Size

| Field          | Size<br>(bytes) | Layer                              | Notes                                                   |

|----------------|-----------------|------------------------------------|---------------------------------------------------------|

| Header         | 2               | Physical,<br>Transport,<br>Logical |                                                         |

| Source ID      | 2               | Transport                          |                                                         |

| Destination ID | 2               | Transport                          |                                                         |

| Trans/wrsize   | 1               | Logical                            |                                                         |

| srcTID         | 1               | Logical                            |                                                         |

| Address        | 8               | Logical                            | Includes Extended_address,<br>Address, Wdptr, and Xambs |

| Payload        | 256             | Logical                            |                                                         |

| CRC            | 4               | Physical                           | Extra two CRC bytes for packets greater than 80 bytes   |

| Total          | 276             |                                    |                                                         |

Blank page

# **Chapter 3 Control Symbols**

### 3.1 Introduction

This chapter specifies RapidIO physical layer control symbols. Control symbols are the message elements used by ports connected by an LP-Serial link to manage all aspects of LP-Serial link operation. They are used for link maintenance, packet delimiting, packet acknowledgment, error reporting, and error recovery. For forward compatibility, control symbols received by a port with a reserved field encoding shall be ignored and not cause an error to be reported.

### 3.2 Control Symbol Field Definitions

This section describes the fields that make up the control symbols.

| Field      | Definition                                                                                                                            |

|------------|---------------------------------------------------------------------------------------------------------------------------------------|

| stype0     | Encoding for control symbols that make use of parameter0 and parameter1. Eight encodings are defined in Table 3-2.                    |

| parameter0 | Used in conjunction with stype0 encodings. Reference Table 3-2 for the description of parameter0 encodings.                           |

| parameter1 | Used in conjunction with stype0 encodings. Reference Table 3-2 for the description of parameter1 encodings.                           |

| stype1     | Encoding for control symbols which make use of the cmd field. The eight encodings are defined in Table 3-6.                           |

| cmd        | Used in conjunction with the stype1 field to define the link maintenance commands. Refer to Table 3-7 for the cmd field descriptions. |

| CRC        | 5-bit code used to detect transmission errors in control symbols. See Section 3.6 for details on the CRC error detection scheme.      |

Table 3-1. Control Symbol Field Definitions

# 3.3 Control Symbol Format

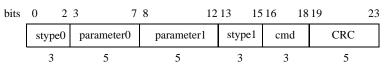

This section describes the general format of the LP-Serial control symbols. Figure 3-1 shows the control symbol format.

Figure 3-1. Packet-Retry Control Symbol Format

All control symbols follow the 24-bit control symbol format as detailed above. The

fields parameter0 and parameter1 are used by the functions encoded in the stype0 field. The cmd field is a modifier for the functions encoded in the stype1 field.

Control symbols can carry two functions, one encoded in the stype0 field and one encoded in the stype1 field. The functions encoded in stype0 are "status" functions that convey some type of status about the port transmitting the control symbol. The functions encoded in stype1 are requests to the receiving port or transmission delimiters.

A control symbol carrying one function is referred to using the name of the function it carries. A control symbol carrying two functions may be referred to using the name of either function that it carries. For example, a control symbol with stype0 set to packet-accepted and stype1 set to NOP is referred to a packet-accepted control symbol. A control symbol with stype0 set to packet-accepted and stype1 set to restart-from-retry is referred to as either a packet-accepted control symbol or a restart-from-retry control symbol depending on which name is appropriate for the context.

Control symbols are specified with the ability to carry two functions so that a packet acknowledgment and a packet delimiter can be carried in the same control symbol. Packet acknowledgment and packet delimiter control symbols constitute the vast majority of control symbol traffic on a busy link. Carrying an acknowledgment (or status) and a packet delimiter whenever possible in a single control symbol allows a significant reduction in link overhead traffic and an increase in the link bandwidth available for packet transmission.

# 3.4 Stype0 Control Symbols

The encoding and function of stype0 and the information carried in parameter0 and parameter1 for each stype0 encoding shall be as specified in Table 3-2.

| atrum o D | Function            | Conte        | Reference   |               |  |

|-----------|---------------------|--------------|-------------|---------------|--|

| stype0    | Function            | Parameter0   | Parameter1  | - Reference   |  |

| 0b000     | Packet-accepted     | packet_ackID | buf_status  | Section 3.4.1 |  |

| 0b001     | Packet-retry        | packet_ackID | buf_status  | Section 3.4.2 |  |

| 0b010     | Packet-not-accepted | packet_ackID | cause       | Section 3.4.3 |  |

| 0b011     | Reserved            | -            | -           | -             |  |

| 0b100     | Status              | ackID_status | buf_status  | Section 3.4.4 |  |

| 0b101     | Reserved            | -            | -           | -             |  |

| 0b110     | Link-response       | ackID_status | port_status | Section 3.4.5 |  |

| 0b111     | Reserved            | -            | -           | -             |  |

Table 3-2. Stype0 Control Symbol Encoding

The status control symbol is the default stype0 encoding and is used when the control symbol does not convey another stype0 function. The following table

defines the parameters valid for stype0 control symbols.

| Parameter    | Definition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| packet_ackID | The ackID of the packet being acknowledged by an acknowledgment control symbol.                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ackID_status | The value of ackID expected in the next packet the port receives. For example, a value of 0b00001 indicates the device is expecting to receive ackID 1.                                                                                                                                                                                                                                                                                                                                                                  |

|              | Specifies the number of maximum length packets that the port can accept without issuing a retry due to a lack of resources. The value of buf_status in a packet-accepted, packet-retry, or status control symbol is the number of maximum packets that can be accepted, inclusive of the effect of the packet being accepted or retried.                                                                                                                                                                                 |

| buf_status   | Value 0-29: The encoding value specifies the number of new maximum sized packets the receiving device can receive. The value 0, for example, signifies that the downstream device has no available packet buffers (thus is not able to hold any new packets). Value 30: The value 30 signifies that the downstream device can receive 30 or more new maximum sized packets. Value 31: The downstream device can receive an undefined number of maximum sized packets, and relies on the retry protocol for flow control. |

#### Table 3-3. Stype0 Parameter Definitions

#### NOTE:

The following sections depict various control symbols. Since control symbols can contain one or two functions, shading in the figures is used to indicate which fields are applicable to that specific control symbol function.

### 3.4.1 Packet-Accepted Control Symbol

The packet-accepted control symbol indicates that the receiving device has taken responsibility for sending the packet to its final destination and that resources allocated by the sending device can be released. This control symbol shall be generated only after the entire packet has been received and found to be free of detectable errors. The packet-accepted control symbol format is displayed in Figure 3-2.

| 0b000 | packet_ackID | buf_status | stype1 | cmd | CRC |

|-------|--------------|------------|--------|-----|-----|

| 3     | 5            | 5          | 3      | 3   | 5   |

Figure 3-2. Packet-Accepted Control Symbol Format

### 3.4.2 Packet-Retry Control Symbol

A packet-retry control symbol indicates that the receiving device was not able to accept the packet due to some temporary resource conflict such as insufficient buffering and the sender should retransmit the packet. This control symbol format is displayed in Figure 3-3.

| 0b001 | packet_ackID | buf_status | stype1 | cmd | CRC |

|-------|--------------|------------|--------|-----|-----|

| 3     | 5            | 5          | 3      | 3   | 5   |

Figure 3-3. Packet-Retry Control Symbol Format

### 3.4.3 Packet-Not-Accepted Control Symbol

The packet-not-accepted control symbol is used to indicate to the sender of a packet why the packet was not accepted by the receiving port. As shown in Figure 3-4, the control symbol contains a cause field that indicates the reason for not accepting the packet and a packet\_ackID field. If the receiving device is not able to specify the cause, or the cause is not one of defined options, the general error encoding shall be used.

| 0b010 | packet_ackID | cause | stype1 | cmd | CRC |

|-------|--------------|-------|--------|-----|-----|

| 3     | 5            | 5     | 3      | 3   | 5   |

Figure 3-4. Packet-Not-Accepted Control Symbol Format

The cause field shall be used to display informational fields useful for debug. Table 3-4 displays the reasons a packet may not be accepted, indicated by the cause field.

| Table 3-4. | Cause | Field | Definition |

|------------|-------|-------|------------|

|------------|-------|-------|------------|

| Cause             | Definition                                                 |

|-------------------|------------------------------------------------------------|

| 0Ь00000           | Reserved                                                   |

| 0b00001           | Received unexpected ackID on packet                        |

| 0b00010           | Received a control symbol with bad CRC                     |

| 0b00011           | Non-maintenance packet reception is stopped                |

| 0b00100           | Received packet with bad CRC                               |

| 0b00101           | Received invalid character, or valid but illegal character |

| 0b00110 - 0b11110 | Reserved                                                   |

| 0b11111           | General error                                              |

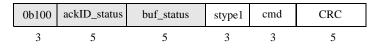

### 3.4.4 Status Control Symbol

The status control symbol is the default stype0 encoding and is used when the control symbol does not convey another stype0 function. The status control symbol contains the ackID\_status and the buf\_status fields. The buf\_status field indicates to the receiving port the number of maximum length packet buffers the sending port had available for packet reception at the time the control symbol was generated. The ackID\_status field allows the receiving port to determine if it and the sending port are in sync with respect to the next ackID value the sending port expects to receive. The status control symbol format is shown in Figure 3-5 below.

### 3.4.5 Link-Response Control Symbol

The link-response control symbol is used by a device to respond to a link-request control symbol as described in the link maintenance protocol described in Section 5.5. The status reported in the status field is the status of the port at the time the associated input-status link-request control symbol was received.

| 0b110 | ackID_status | port_status | stype1 | cmd | CRC |

|-------|--------------|-------------|--------|-----|-----|

| 3     | 5            | 5           | 3      | 3   | 5   |

Figure 3-6. Link-Response Control Symbol Format

The port\_status field of the link-response control symbol is defined in Table 3-5. Table 3-5. Port\_status Field Definitions

| Port_status       | Status        | Description                                                                                                    |

|-------------------|---------------|----------------------------------------------------------------------------------------------------------------|

| 0b00000           |               | Reserved                                                                                                       |

| 0b00001           |               | Reserved                                                                                                       |

| 0b00010           | Error         | The port has encountered an unrecoverable error and is unable to accept packets.                               |

| 0b00011           |               | Reserved                                                                                                       |

| 0b00100           | Retry-stopped | The port has retried a packet and is waiting in the input retry-stopped state to be restarted.                 |

| 0b00101           | Error-stopped | The port has encountered a transmission error and is waiting in the input error-stopped state to be restarted. |

| 0b00110 - 0b01111 |               | Reserved                                                                                                       |

| 0b10000           | ОК            | The port is accepting packets                                                                                  |

| 0b10001 - 0b11111 |               | Reserved                                                                                                       |

# 3.5 Stype1 Control Symbols

The encoding of stype1 and the function of the cmd field are defined in Table 3-6. Table 3-6. Stype1 Control Symbol Encoding

| stype1 | stype1<br>Function | cmd           | cmd<br>Function | Packet<br>Delimiter | Reference       |

|--------|--------------------|---------------|-----------------|---------------------|-----------------|

| 0b000  | Start-of-packet    | 0b000         | -               | yes                 | Section 3.5.1   |

| 0b001  | Stomp              | 0b000         | -               | yes                 | Section 3.5.2   |

| 0b010  | End-of-packet      | 0b000         | -               | yes                 | Section 3.5.3   |

| 0b011  | Restart-from-retry | 0b000         | -               | *                   | Section 3.5.4   |

| 0b100  | Link-request       | 0b000 - 0b010 | Reserved        | *                   | -               |

|        |                    | 0b011         | Reset-device    |                     | Section 3.5.5.1 |

|        |                    | 0b100         | Input-status    |                     | Section 3.5.5.2 |

|        |                    | 0b101- 0b111  | Reserved        |                     | -               |

| 0b101  | Multicast-event    | 0b000         | -               | No                  | Section 3.5.6   |

| 0b110  | Reserved           | 0b000         | -               | No                  | -               |

| 0b111  | NOP (Ignore) **    | 0b000         | -               | No                  | -               |

Note: \* denotes that restart-from-retry and link-request control symbols may only be packet delimiters if a packet is in progress.

Note: **\*\*** NOP (Ignore) is not defined as a control symbol, but is the default value when the control symbol does not convey another stype1 function.

#### NOTE:

The following sections depict various control symbols. Since control symbols can contain one or two functions, shading in the figures is used to indicate which fields are applicable to that specific control symbol function.

### 3.5.1 Start-of-Packet Control Symbol

The start-of-packet control symbol format is shown in Figure 3-7 below.

| stype0 | parameter0 | parameter1 | 0b000 | 0b000 | CRC |

|--------|------------|------------|-------|-------|-----|

| 3      | 5          | 5          | 3     | 3     | 5   |

Figure 3-7. Start-of-Packet Control Symbol Format

### 3.5.2 Stomp Control Symbol

The stomp control symbol is used to cancel a partially transmitted packet. The protocol for packet cancelation is specified in Section 5.8. The stomp control symbol format is shown in Figure 3-8 below.

| stype0 | parameter0 | parameter1 | 0b001 | 0b000 | CRC |

|--------|------------|------------|-------|-------|-----|

| 3      | 5          | 5          | 3     | 3     | 5   |

#### Figure 3-8. Stomp Control Symbol Format

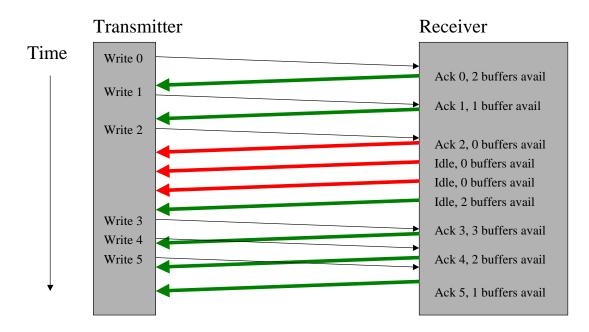

### 3.5.3 End-of-Packet Control Symbol